分类

商品

- 商品

- 店铺

- 资讯

......

...... 基本信息

基本信息 | 商品名称: | 开本: | 16开 | |

| 作者: | 徐文波, 田耘编著 | 定价: | 69.00 |

| ISBN号: | 9787302286431 | 出版时间: | 2012-07-01 |

| 出版社: | 清华大学出版社 | 印刷时间: | 2022-08-01 |

| 版次: | 2 | 印次: | 15 |

1.2.3软核、硬核及固核

1.2.4Xilinx主流FPGA

1.3Xilinx软件工具

1.3.1ISE Foundation软件

1.3.2EDK开发工具

1.3.3System Generator DSP工具

1.3.4ChipScope Pro

1.3.5PlanAhead

1.4本书案例验证平台--S6 CARD开发板

1.4.1S6 CARD开发板的组成与功能

1.4.2S6 CARD板卡引脚约束说明

本章小结

第2章Verilog HDL开发基础与进阶

2.1Verilog HDL语言

2.1.1Verilog HDL语言的历史

2.1.2Verilog HDL的主要功能

2.1.3Verilog HDL和VHDL的区别

2.1.4Verilog HDL设计方法

2.2Verilog HDL基本程序结构

2.3Verilog HDL语言的数据类型和运算符

2.3.1标志符

2.3.2数据类型

2.3.3模块端口

2.3.4常量集合

2.3.5运算符和表达式

2.4Verilog HDL语言的描述语句

2.4.1结构描述形式

2.4.2数据流描述形式

2.4.3行为描述形式

2.4.4混合设计模式

2.5Verilog HDL建模与调试技巧

2.5.1双向端口的使用和仿真

2.5.2阻塞赋值与非阻塞赋值

2.5.3输入值不确定的组合逻辑电路

2.5.4数学运算中的扩位与截位操作

2.5.5利用块RAM来实现数据延迟

2.5.6测试向量的生成

2.6Verilog HDL常用程序示例

2.6.1数字电路中基本单元的FPGA实现

2.6.2基本时序处理模块

2.7Xilinx器件原语的使用

本章小结

第3章Xilinx FPGA电路原理与系统设计

3.1FPGA配置电路

3.1.1Xilinx FPGA配置电路

3.1.2Xilinx FPGA常用的配置引脚

3.1.3Xilinx FPGA配置电路分类

3.2JTAG电路的原理与设计

3.2.1JTAG电路的工作原理

3.2.2Xilinx JTAG下载线

3.3FPGA的常用配置电路

3.3.1主串模式--常用的FPGA配置模式

3.3.2SPI串行Flash配置模式

3.3.3从串配置模式

3.3.4主字节宽度并行配置模式

3.3.5JTAG配置模式

3.3.6System ACE配置方案

3.4iMPACT软件使用

3.4.1iMPACT软件

3.4.2iMPACT中的JTAG配置操作

3.4.3iMPACT中的Xilinx PROM配置操作

3.4.4iMPACT中的SPI Flash配置操作

3.4.5FPGA配置失败的常见问题

3.5从配置PROM中读取用户数据

3.5.1从PROM中引导数据

3.5.2硬件电路设计方法

3.5.3软件操作流程

本章小结

第4章基于ISE Foundation的逻辑设计

4.1ISE套件

4.1.1ISE的特点

4.1.2ISE的功能

4.1.3ISE的安装

4.1.4ISE的用户界面

4.2基于ISE的设计输入

4.2.1新建工程

4.2.2代码输入

4.2.3代码模板的使用

4.2.4Xilinx IP Core的原理与应用

4.3ISE基本操作

4.3.1基于Xilinx XST的综合

4.3.2基于ISim的仿真

4.3.3基于ISE的实现

4.3.4基于目标和策略的设计方法

4.3.5基于SmartGuide的设计方法

4.3.6比特文件的生成

4.3.7基于IMPACT的芯片配置

4.3.8功耗分析以及XPower的使用

4.4约束

4.4.1约束文件

4.4.2UCF文件的语法说明

4.4.3引脚和区域约束语法

4.4.4时序约束语法

4.5调试利器--ChipScope Pro

4.5.1ChipScope Pro工作原理

4.5.2ChipScope Pro操作流程

4.5.3ChipScope Pro开发实例

4.6ISE与第三方EDA软件

4.6.1ModelSim软件的使用

4.6.2ModelSim和ISE的联合开发流程

4.6.3MATLAB软件的使用

4.6.4ISE与MATLAB的联合使用

4.6.5MATLAB、ModelSim和ISE联合开发实例

本章小结

第5章时序分析

5.1时序分析的作用和原理

5.1.1时序分析的作用

5.1.2静态时序分析原理

5.1.3时序分析的基础知识

5.2Xilinx FPGA中的时钟资源

5.2.1全局时钟资源

5.2.2第二全局时钟资源

5.3ISE时序分析器

5.3.1时序分析器的特点

5.3.2时序分析器的文件类型

5.3.3时序分析器的调用与用户界面

5.3.4提高时序性能的手段

本章小结

第6章逻辑开发专题

6.1Verilog HDL设计进阶

6.1.1面向硬件的程序设计思维

6.1.2“面积”和“速度”的转换原则

6.1.3同步电路的设计原则

6.2Xilinx FPGA芯片底层单元的使用

6.2.1Xilinx全局时钟网络的使用

6.2.2CMT时钟管理模块的使用

6.2.3Xilinx内嵌块存储器的使用

6.2.4硬核乘加器的使用

6.3代码风格

6.3.1代码风格的含义

6.3.2代码书写风格

6.3.3通用设计代码风格

6.3.4Xilinx专用设计代码风格

6.4UART接口开发实例

6.4.1串口接口与RS?232协议

6.4.2串口通信控制器的Verilog HDL实现

6.4.3RS?232设计板级调试

本章小结

第7章基于EDK的嵌入式系统设计

7.1可配置嵌入式系统(EDK)

7.1.1基于FPGA的可编程嵌入式开发系统

7.1.2Xilinx公司的解决方案

7.2Xilinx嵌入式开发系统组成

7.2.1片内微处理器软核MicroBlaze

7.2.2PLB总线系统结构

7.2.3IP核以及设备驱动

7.3EDK软件

7.3.1EDK设计的实现流程

7.3.2EDK的文件管理架构

7.4XPS软件典型操作

7.4.1XPS的启动

7.4.2利用BSB创建新工程

7.4.3XPS的用户界面

7.4.4XPS的目录结构与硬件平台

7.4.5在XPS加入IP Core

7.4.6XPS工程的综合与实现

7.5SDK软件典型操作

7.5.1SDK的用户界面

7.5.2SDK的典型操作

7.5.3IP外设的API函数查阅和使用方法

7.5.4GPIO外设开发实例

7.5.5其他外设开发实例

本章小结

第8章基于System Generator的DSP系统设计

8.1System Generator的特点与安装

8.1.1System Generator的主要特点

8.1.2System Generator的安装和配置

8.2System Generator的使用基础

8.2.1System Generator开发流程

8.2.2Simulink的应用

8.3基于System Generator的DSP系统设计

8.3.1System Generator的应用

8.3.2System Generator中的信号类型

8.3.3自动代码生成

8.3.4编译MATLAB设计生成FPGA代码

8.3.5子系统的建立与ISE调用

8.4基于System Generator的硬件协仿真

8.4.1硬件协仿真平台的特点与平台安装

8.4.2硬件协仿真的基本操作

8.4.3共享存储器的操作

8.5System Generator的应用

8.5.1导入外部的HDL程序模块

8.5.2设计在线调试

8.5.3系统中的多时钟设计

8.5.4FPGA设计的技巧

本章小结

第9章数字信号处理专题

9.1数字信号

9.1.1数字信号的产生

9.1.2采样定理

9.1.3数字系统的主要性能指标

9.1.4A/D转换的字长效应

9.2常用DSP IP Core及其应用

9.2.1DDS模块IP Core的应用

9.2.2FFT算法IP Core的应用

9.2.3Cordic算法IP Core的应用

9.2.4FIR滤波器IP Core的应用

9.3多速率滤波器的FPGA实现

9.3.1多速率信号处理的意义

9.3.2多速率信号滤波器的基本操作

9.3.3CIC滤波器的FPGA实现

9.3.4HB滤波器的FPGA实现

本章小结

0章SERDES技术专题

10.1高速数据连接功能

10.1.1高速数据传输

10.1.2Xilinx公司高速连接功能的解决方案

10.2实现吉比特高速串行I/O的相关技术

10.2.1吉比特高速串行I/O的特点和应用

10.2.2吉比特串行I/O系统的组成

10.2.3吉比特串行I/O的设计要点

10.3Rocket I/O收发器原理与开发

10.3.1Rocket I/O硬核组成与工作原理

10.3.2GTP硬核组成与工作原理

10.3.3GTP Wizard开发实例

10.4PCI?Express G1端点接口设计

10.4.1PCI Express G1技术

10.4.2Xilinx PCI Express G1端点模块

10.4.3PCI Express G1端点接口实例解读

本章小结

参考文献

......

...... 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、VerilogHDL开发基础与进阶、Xilinx FPGA电路原理与系统设计、基于ISEFoundation的逻辑设计、时序分析、逻辑开发专题、基于EDK的嵌入式系统设计、基于SystemGenerator的DSP系统设计、数字信号处理专题以及SERDES技术专题共10章。各章均以实战开发为目的,结合*版本的软硬件特征,覆盖了FPGA的各主要应用领域。配套光盘中包含了书中所有的实例代码,便于读者快速动手实践。书中融汇了作者多年的工程开发经验,希望能够极力帮助读者提高工程开发能力。

本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、VerilogHDL开发基础与进阶、Xilinx FPGA电路原理与系统设计、基于ISEFoundation的逻辑设计、时序分析、逻辑开发专题、基于EDK的嵌入式系统设计、基于SystemGenerator的DSP系统设计、数字信号处理专题以及SERDES技术专题共10章。各章均以实战开发为目的,结合*版本的软硬件特征,覆盖了FPGA的各主要应用领域。配套光盘中包含了书中所有的实例代码,便于读者快速动手实践。书中融汇了作者多年的工程开发经验,希望能够极力帮助读者提高工程开发能力。 ......

...... ......

......

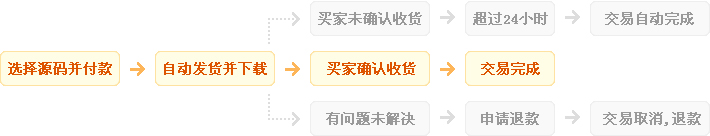

发货方式

自动:在特色服务中标有自动发货的商品,拍下后,源码类 软件类 商品会在订单详情页显示来自卖家的商品下载链接,点卡类 商品会在订单详情直接显示卡号密码。

手动:未标有自动发货的的商品,付款后,商品卖家会收到平台的手机短信、邮件提醒,卖家会尽快为您发货,如卖家长时间未发货,买家也可通过订单上的QQ或电话主动联系卖家。

退款说明

1、源码类:商品详情(含标题)与实际源码不一致的(例:描述PHP实际为ASP、描述的功能实际缺少、功能不能正常使用等)!有演示站时,与实际源码不一致的(但描述中有"不保证完全一样、可能有少许偏差"类似显著公告的除外);

2、营销推广类:未达到卖家描述标准的;

3、点卡软件类:所售点卡软件无法使用的;

3、发货:手动发货商品,在卖家未发货前就申请了退款的;

4、服务:卖家不提供承诺的售后服务的;(双方提前有商定和描述中有显著声明的除外)

5、其他:如商品或服务有质量方面的硬性常规问题的。未符合详情及卖家承诺的。

注:符合上述任一情况的,均支持退款,但卖家予以积极解决问题则除外。交易中的商品,卖家无法修改描述!

注意事项

1、在付款前,双方在QQ上所商定的内容,也是纠纷评判依据(商定与商品描述冲突时,以商定为准);

2、源码商品,同时有网站演示与商品详情图片演示,且网站演示与商品详情图片演示不一致的,默认按商品详情图片演示作为纠纷评判依据(卖家有特别声明或有额外商定的除外);

3、点卡软件商品,默认按商品详情作为纠纷评判依据(特别声明或有商定除外);

4、营销推广商品,默认按商品详情作为纠纷评判依据(特别声明或有商定除外);

5、在有"正当退款原因和依据"的前提下,写有"一旦售出,概不支持退款"等类似的声明,视为无效声明;

6、虽然交易产生纠纷的几率很小,卖家也肯定会给买家最完善的服务!但请买卖双方尽量保留如聊天记录这样的重要信息,以防产生纠纷时便于送码网快速介入处理。

送码声明

1、送码网作为第三方中介平台,依据双方交易合同(商品描述、交易前商定的内容)来保障交易的安全及买卖双方的权益;

2、非平台线上交易的项目,出现任何后果均与送码网无关;无论卖家以何理由要求线下交易的(如:要求买家支付宝转账付款的,微信转账付款的等),请联系管理举报,本平台将清退卖家处理。

¥215.00

¥215.00

正版 steam 原子之心 Atomic Heart 国区激活码 cd...

¥269.00

¥269.00

steam 英雄连3 国区激活码CDKEY PC游戏正版 Compan...

¥734.95

¥734.95

M,日朋礼送男友老公创意实人用星人际机器蓝牙音箱走心情节生礼...

¥285.00

¥285.00

zippo之宝官方正品打火机古银双面贴章机器人煤油机送男友礼物女...

¥88.00

¥88.00

秋季圆领卫衣套头男友风秋天长袖时尚潮流印花卡通机器派大星上衣...

¥98.00

¥98.00

机器猫情侣衬衫小叮当落肩短袖衬衣男友外套大码潮流套装上衣薄款...

¥568.00

¥568.00

PDPAOLA小机器人情侣手链女男生日礼物520送男友男士款闺蜜Rob...

¥9.00

¥9.00

兼容乐高复仇者联盟4战争机器积木人仔钢铁侠救援机甲玩具WM723...

¥12.9

¥12.9

兼容乐高复联4钢铁侠X0252灭霸MK50 MK1战争机器拼装积木人仔...

¥26.8

¥26.8

XBOX ONE SERIES X|S 中文 战争机器4与光环5守护...

¥35.00

¥35.00

Steam正版 中文PC游戏acc神力科莎:争锋 竞速 Assetto...

¥11.5

¥11.5

PC中文正版 Steam 这是我的战争 This War of Min...

¥30.00

¥30.00

爱奇艺黄金vip会员1个月视频会员iqiyi月卡 手机号直充不支持电视...

¥220.8

¥220.8

乐高机械结构设计+乐高仿生机器人设计+乐高简单机械创意设计+乐高炫酷机...

¥168.00

¥168.00

优彼早教机优比故事机儿歌播放器儿童智能机器人婴儿启蒙益智玩具...

¥128.00

¥128.00

正版《上古卷轴V天际 天际图书馆 卷三 奥术》第3册 官方设定集第三卷...

¥48.00

¥48.00

iphone14手机壳镜面玻璃苹果14promax保护套兔子化妆镜苹果...

¥99.00

¥99.00

谷歌开源编程golang语言程序员IT技术开发连帽卫衣男生上衣服帽衫...

¥8.2

¥8.2

STM8S 电子开发板 小系统板 STM8S103F3P6 单片机核心...

¥23.92

¥23.92

2023版小学学霸一二年级三年级四4五5六上册下册语文数学英语人教版北...